AI Chip Architecture

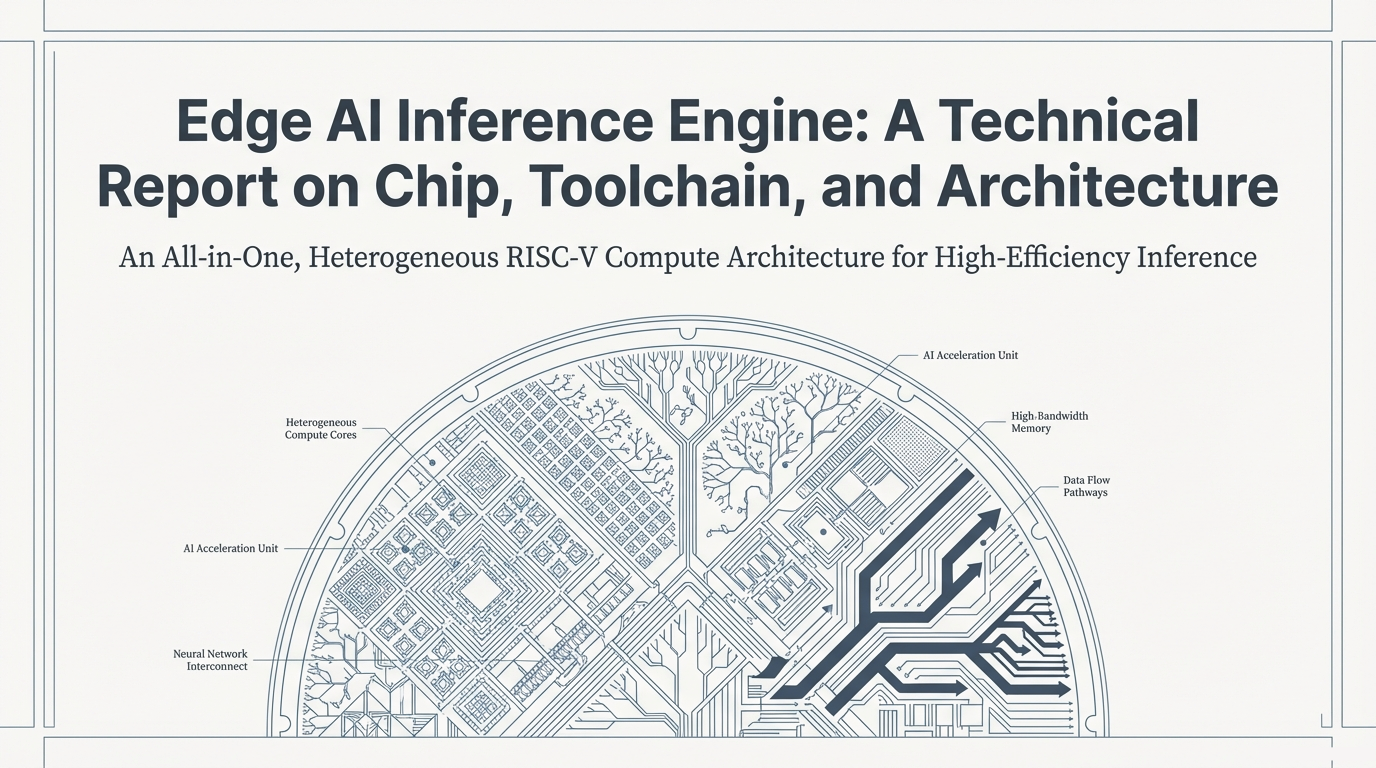

Edge AI Inference Engine

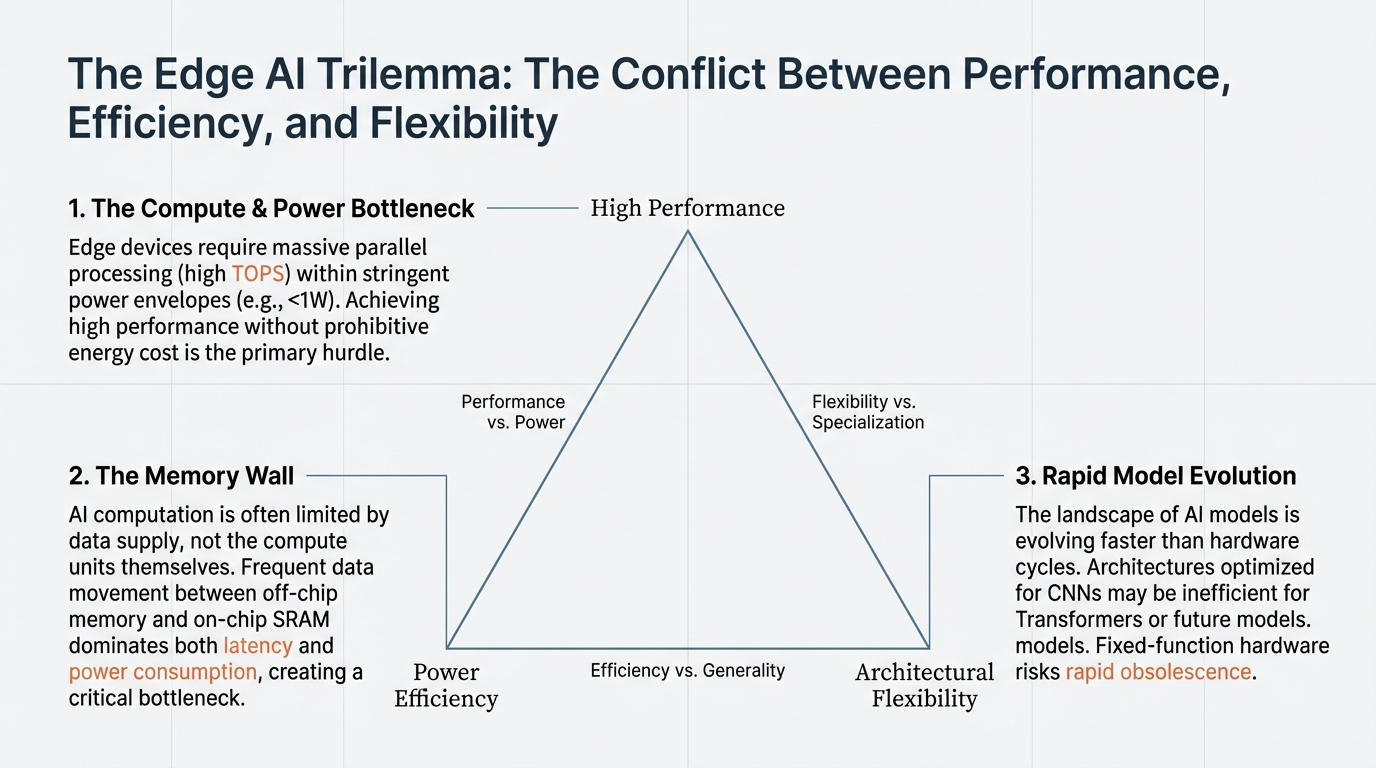

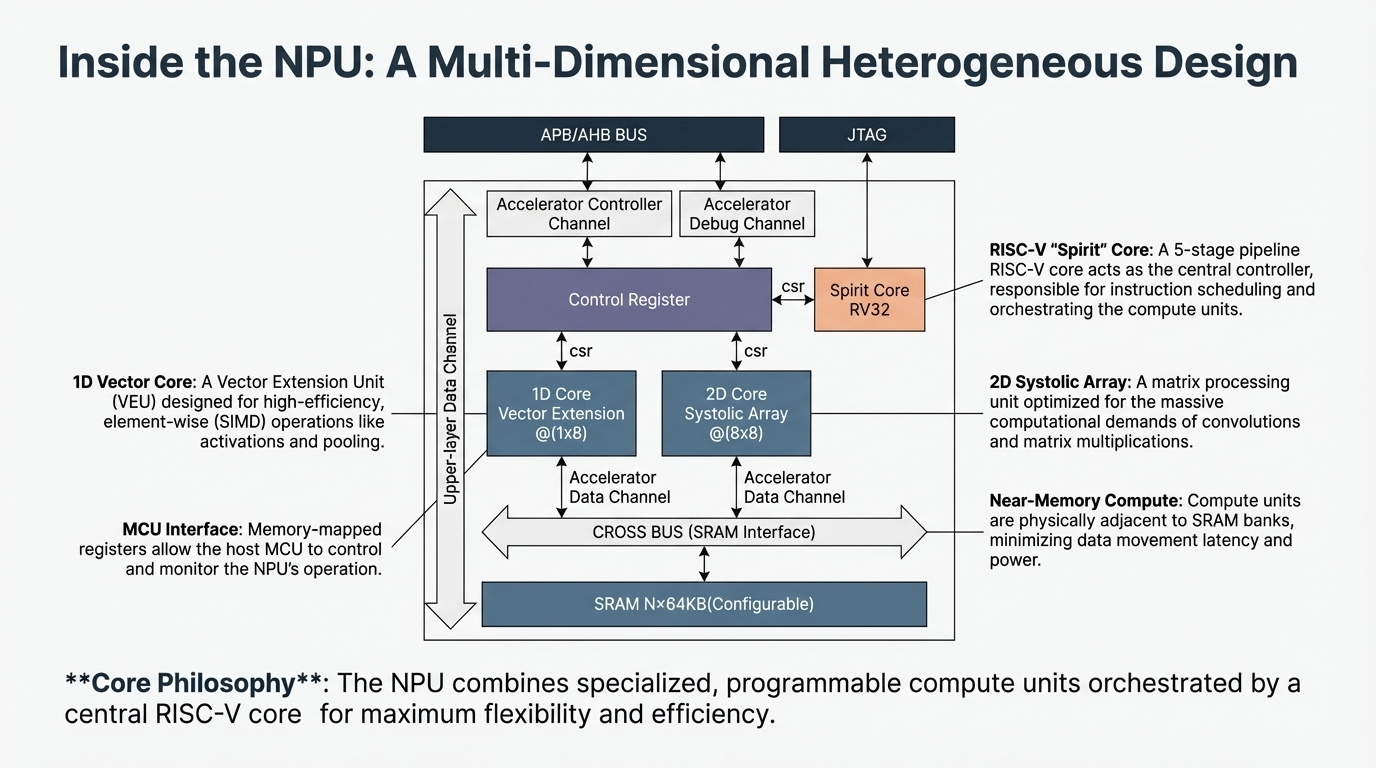

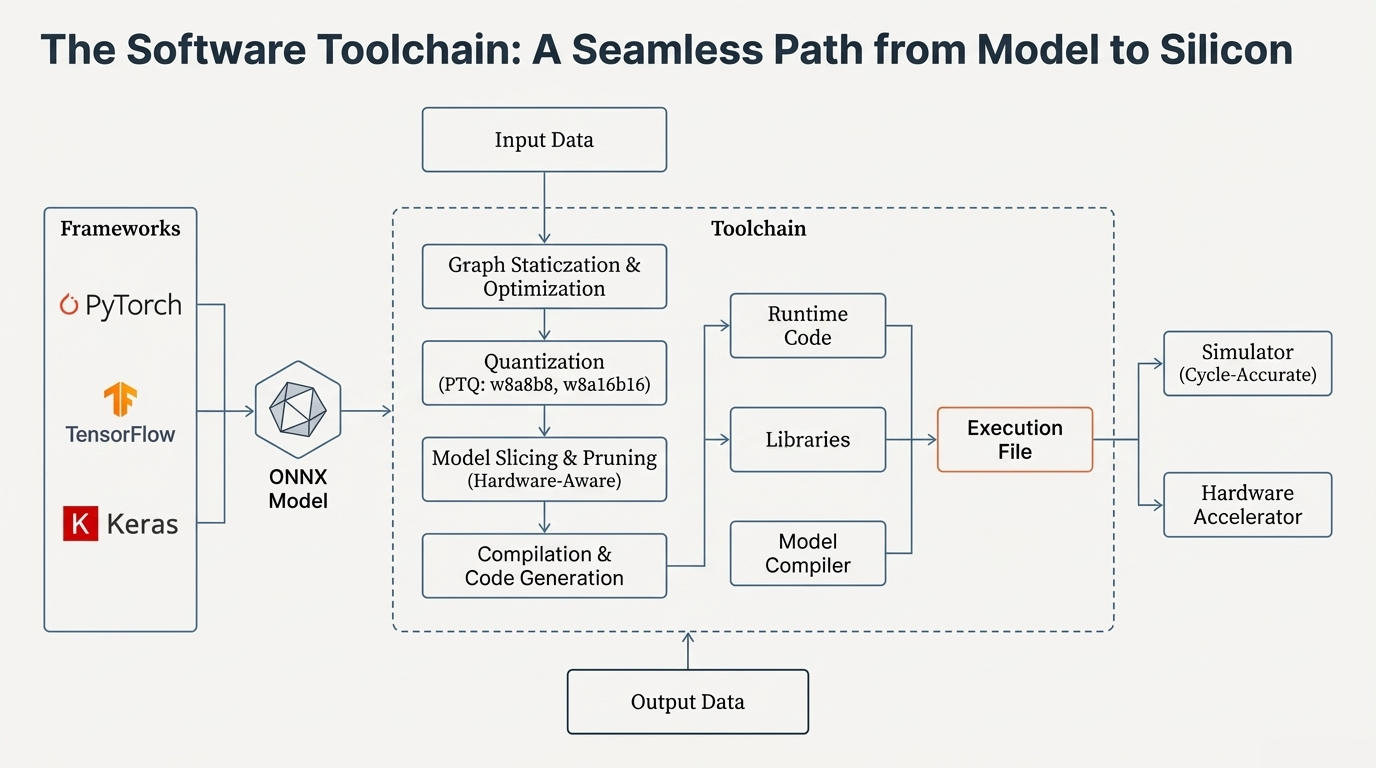

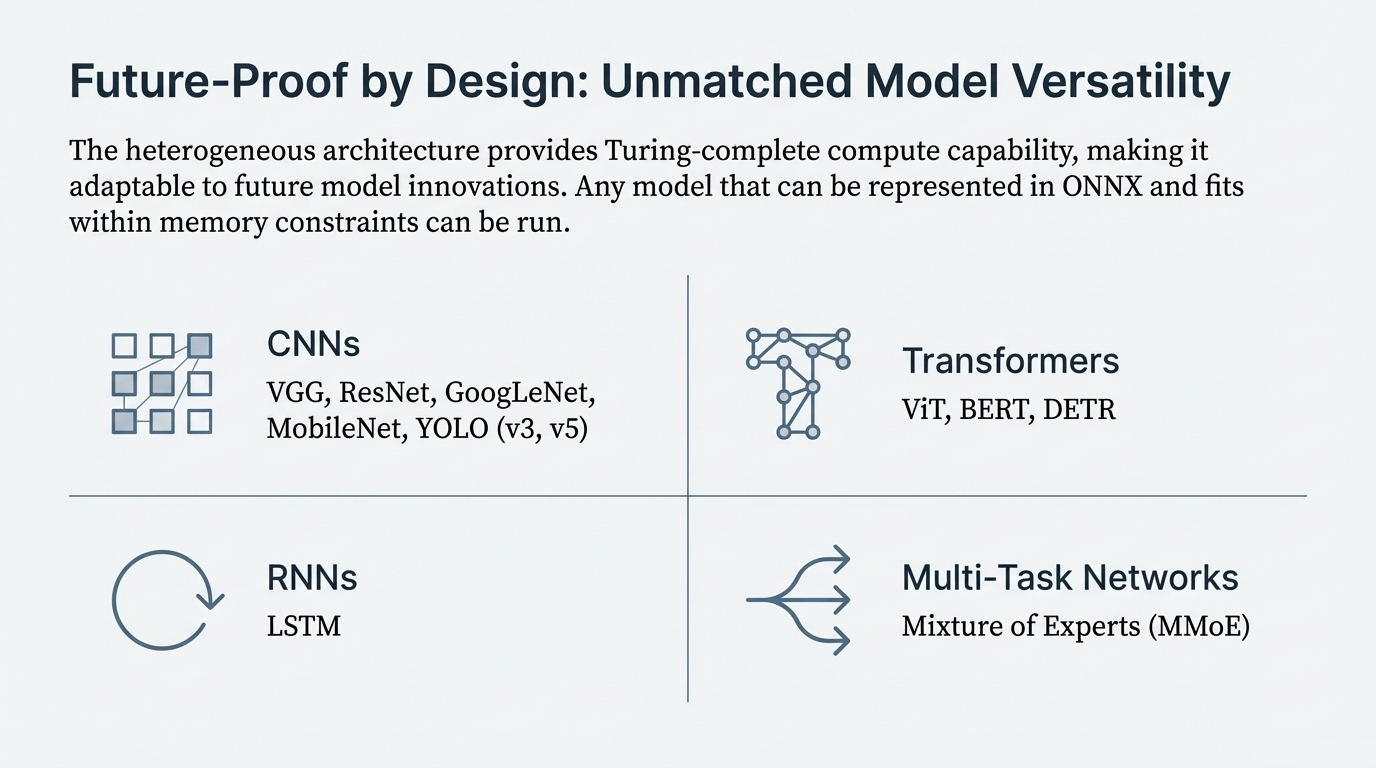

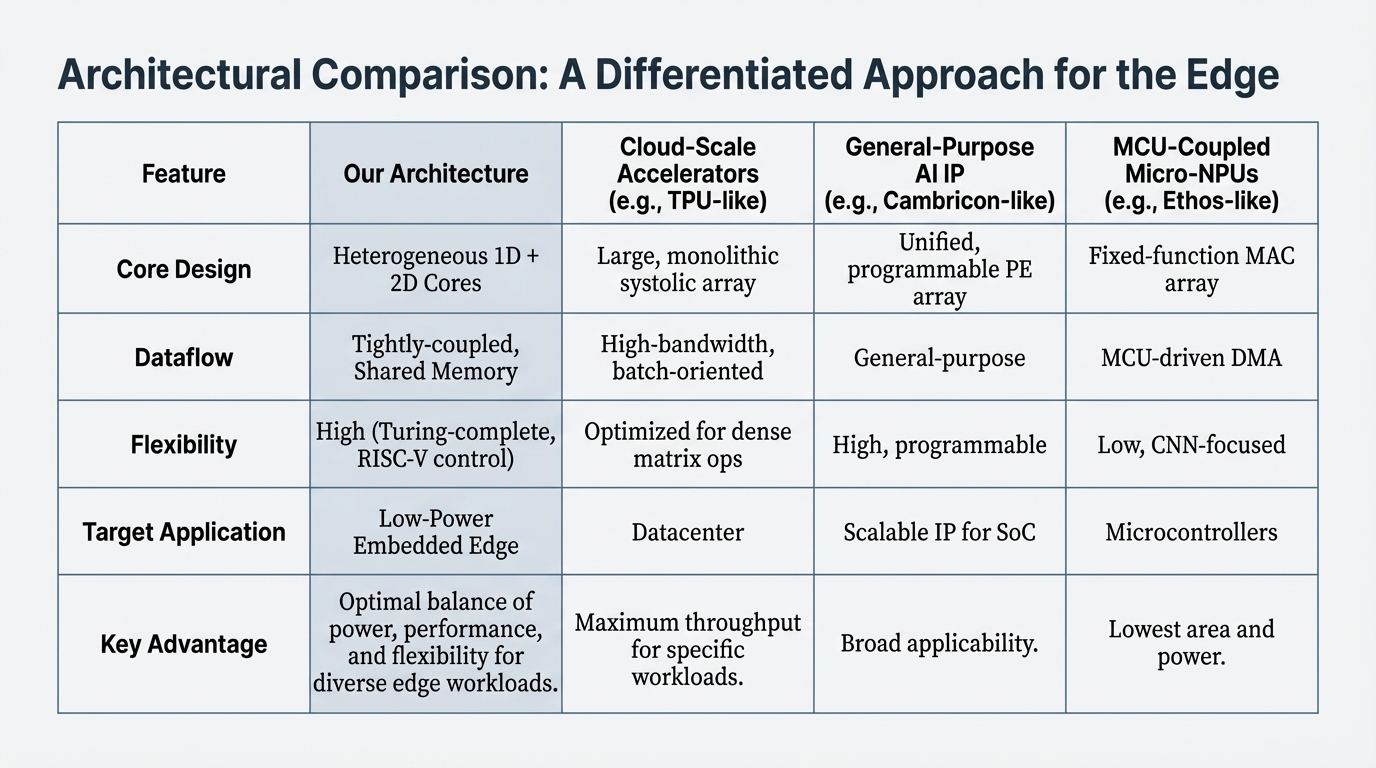

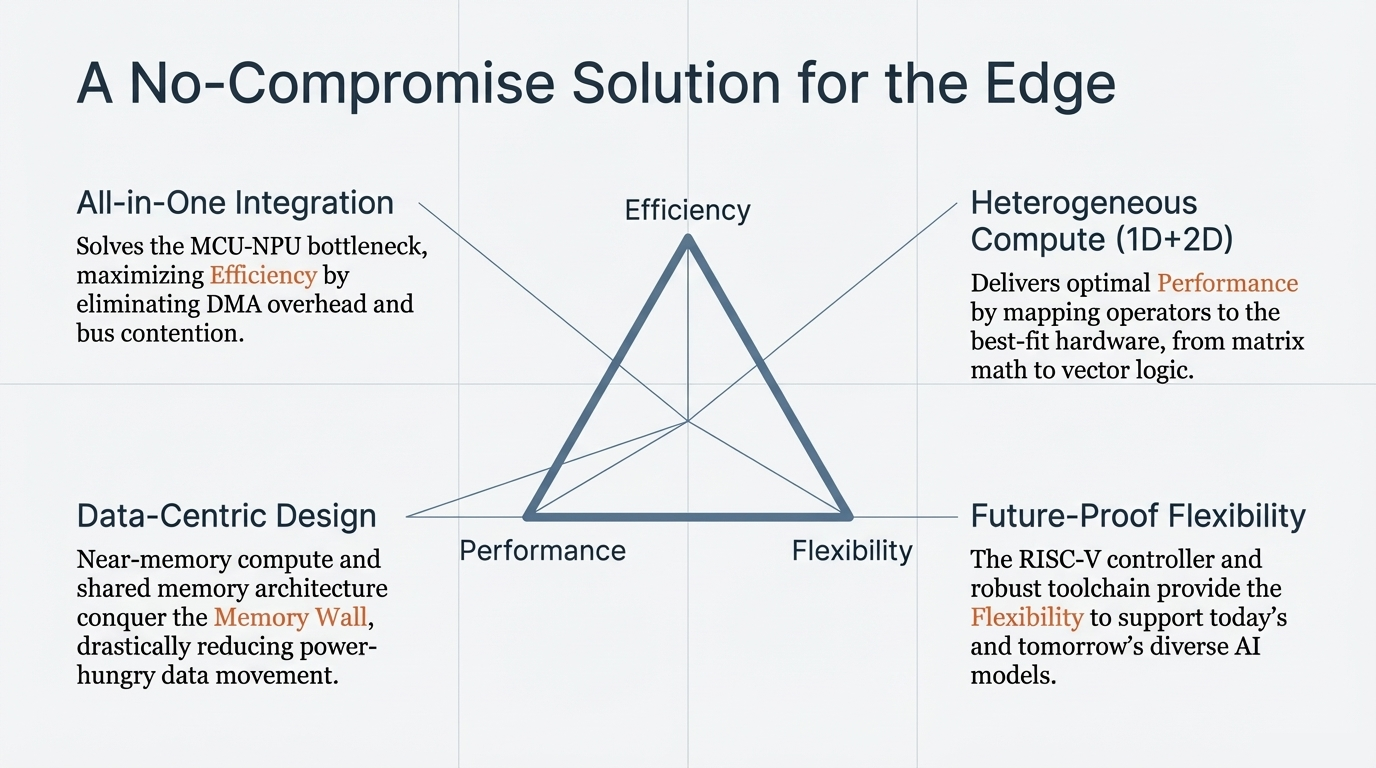

Addressing the “Edge AI Trilemma” of performance, efficiency, and flexibility, this report introduces a novel Heterogeneous RISC-V Compute Architecture.

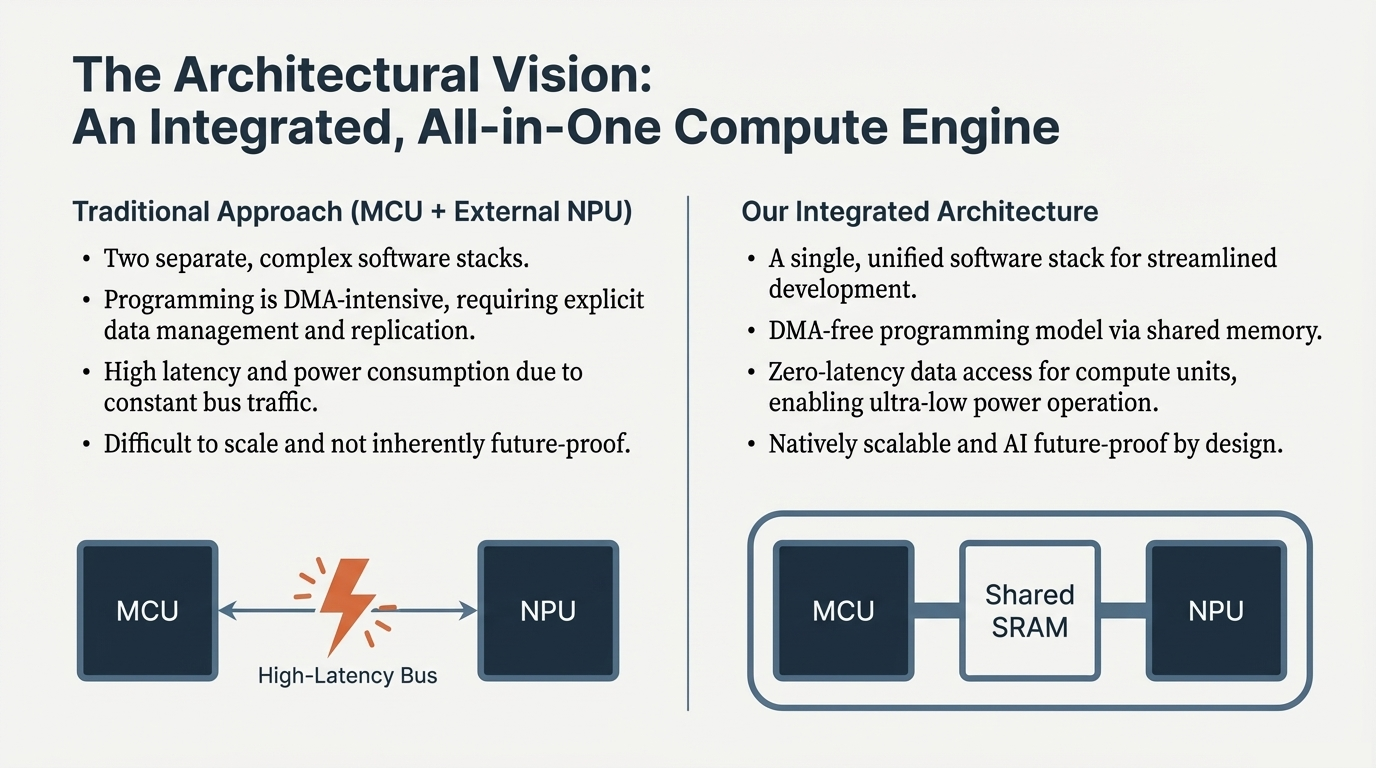

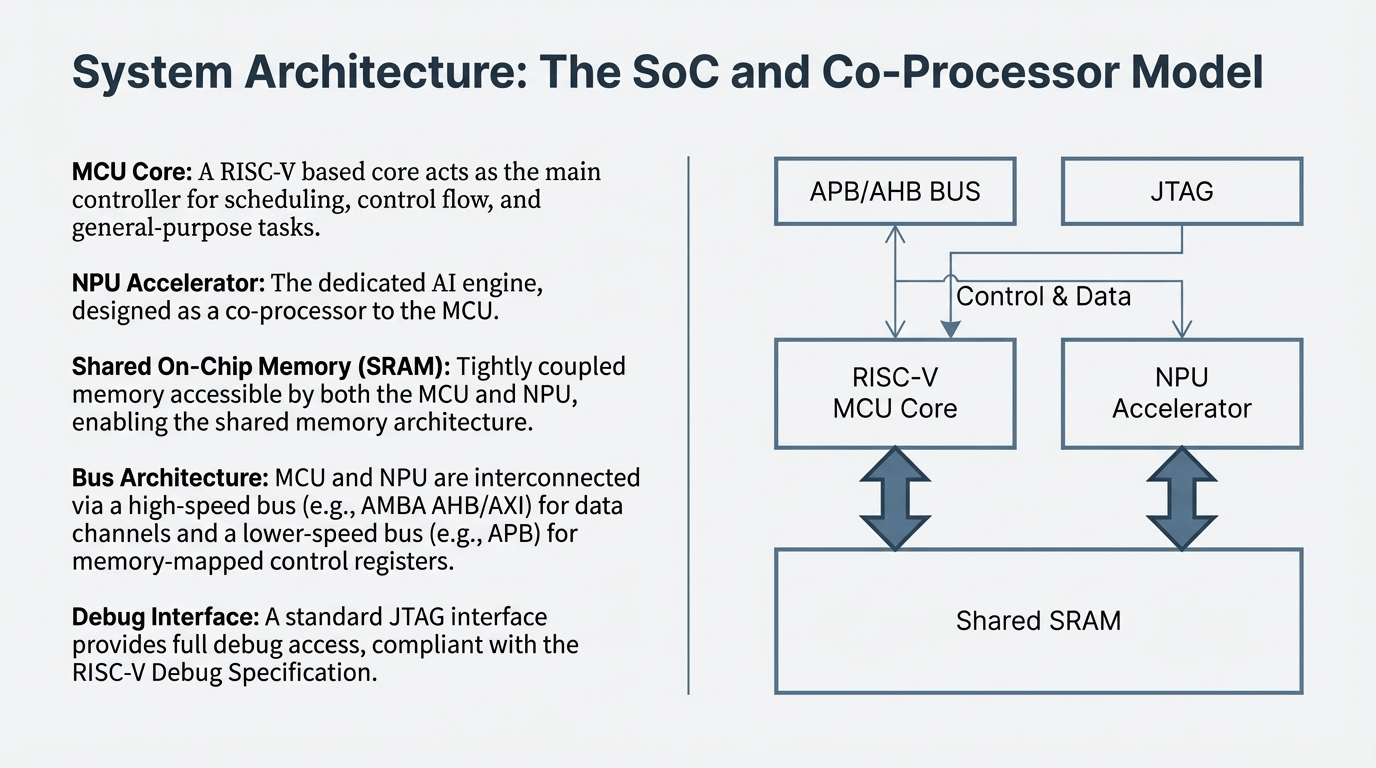

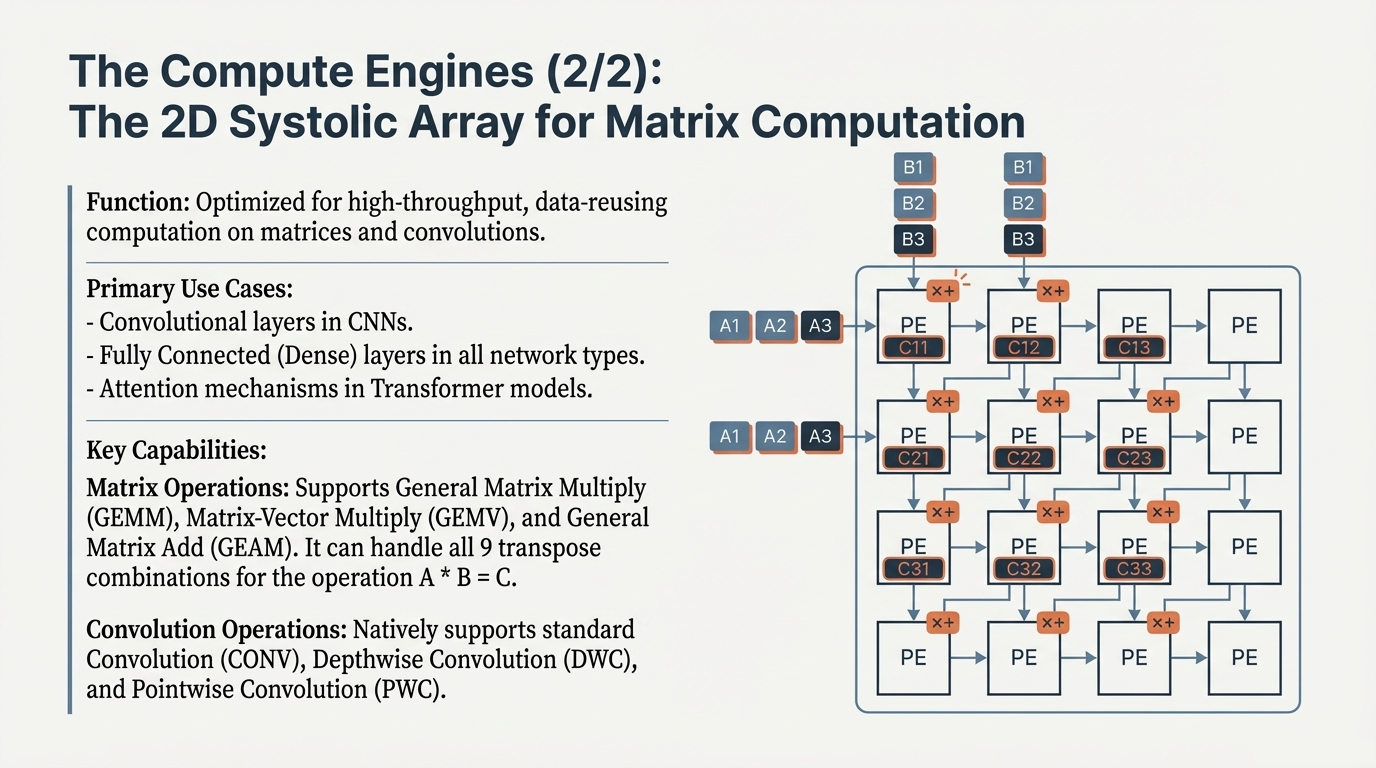

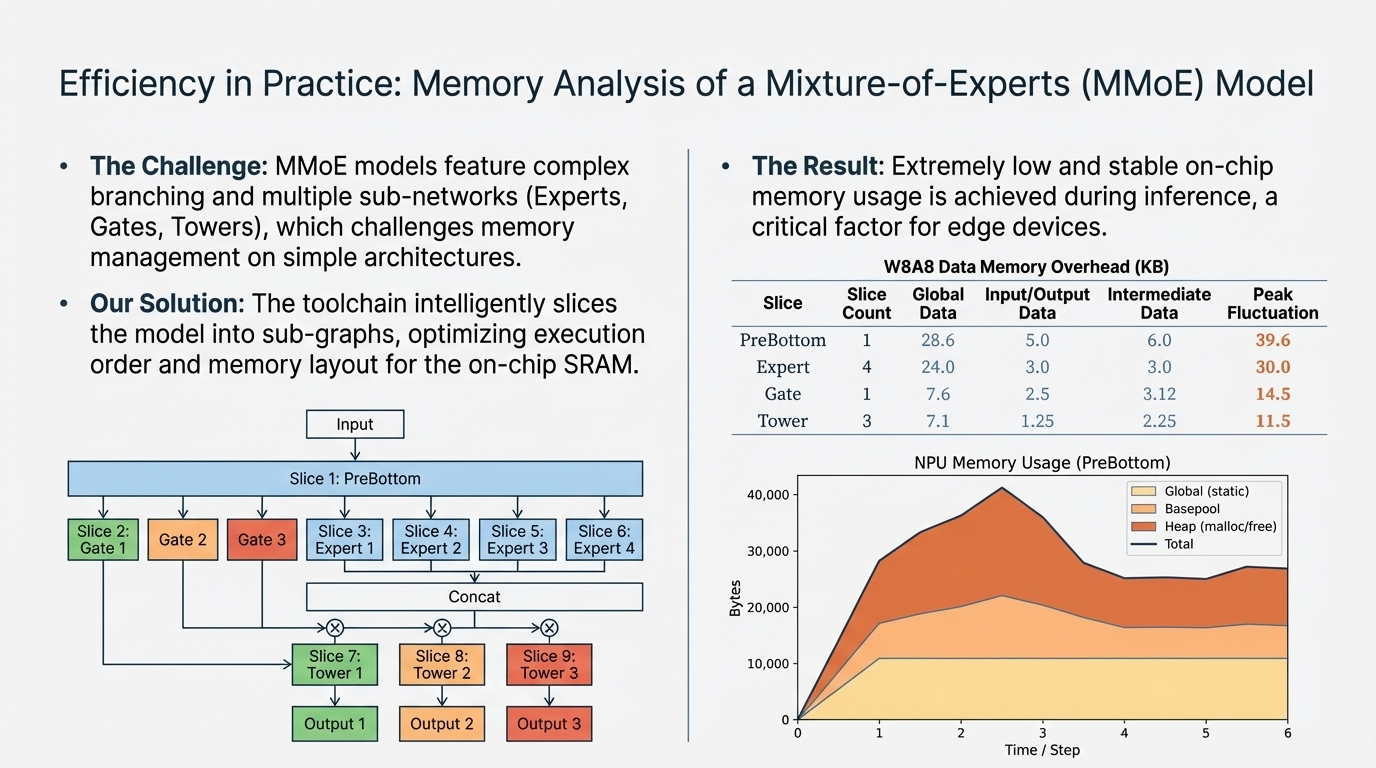

Our “All-in-One” design integrates a 1D Vector Core and a 2D Systolic Array with shared SRAM, effectively breaking the “Memory Wall” bottleneck. This architecture eliminates high-latency bus traffic, achieving ultra-low power consumption (<1W) while maintaining the flexibility to support rapidly evolving models from CNNs to Transformers.

1 / 13

2 / 13

3 / 13

4 / 13

5 / 13

6 / 13

7 / 13

8 / 13

9 / 13

10 / 13

11 / 13

12 / 13

13 / 13

End of Report

Use arrow keys to navigate