📜A Domain Specific Computing Architecture for Open 6G Baseband Signal Processing

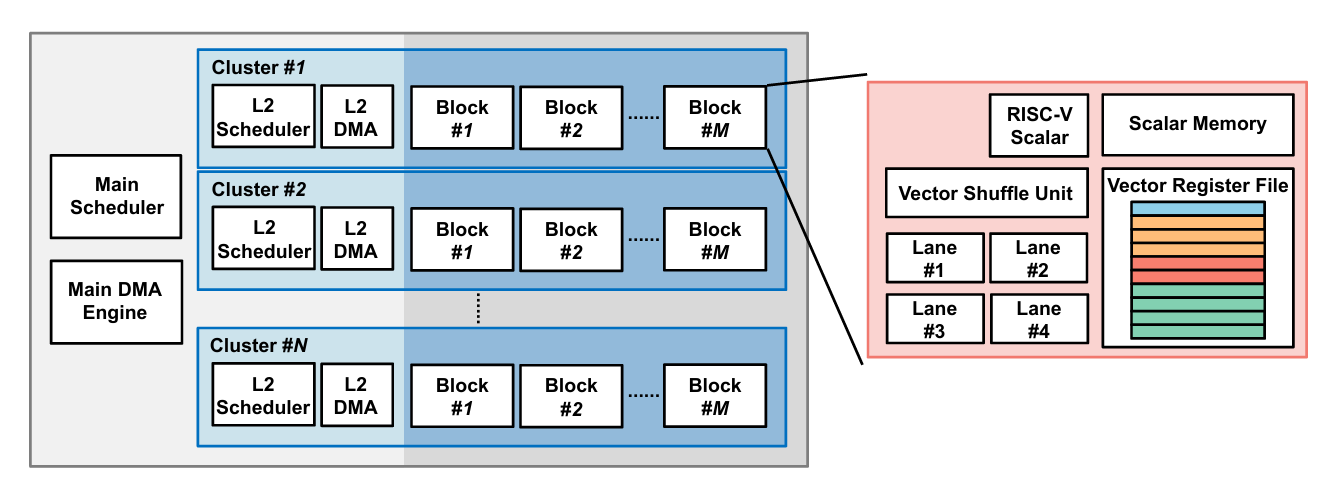

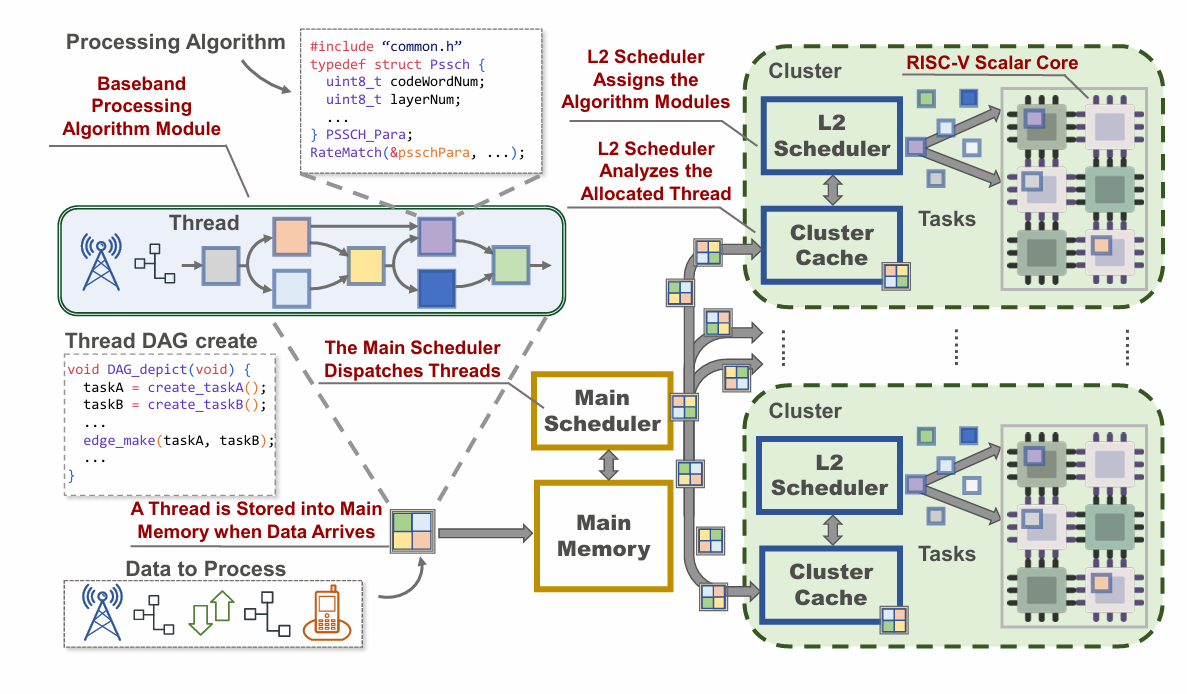

At the ACM Turing Award Celebration Conference 2023 - China (TURC ‘23), we introduced a domain-specific manycore architecture optimized for future 6G baseband signal processing. Built upon RISC-V instruction extensions and a multi-level dataflow programming model, our design achieves moderate performance while offering flexible software programmability. By integrating custom instructions like complex multiplication and parallel shuffle, the architecture accelerates key signal processing tasks and addresses the energy and flexibility limitations of general-purpose processors (GPPs), digital signal processors (DSPs), and field-programmable gate arrays (FPGAs).

Check out our paper at : https://dl.acm.org/doi/10.1145/3603165.3607377