📜Zoozve: A Strip-Mining-Free RISC-V Vector Extension with Arbitrary Register Grouping Compilation Support (WIP)

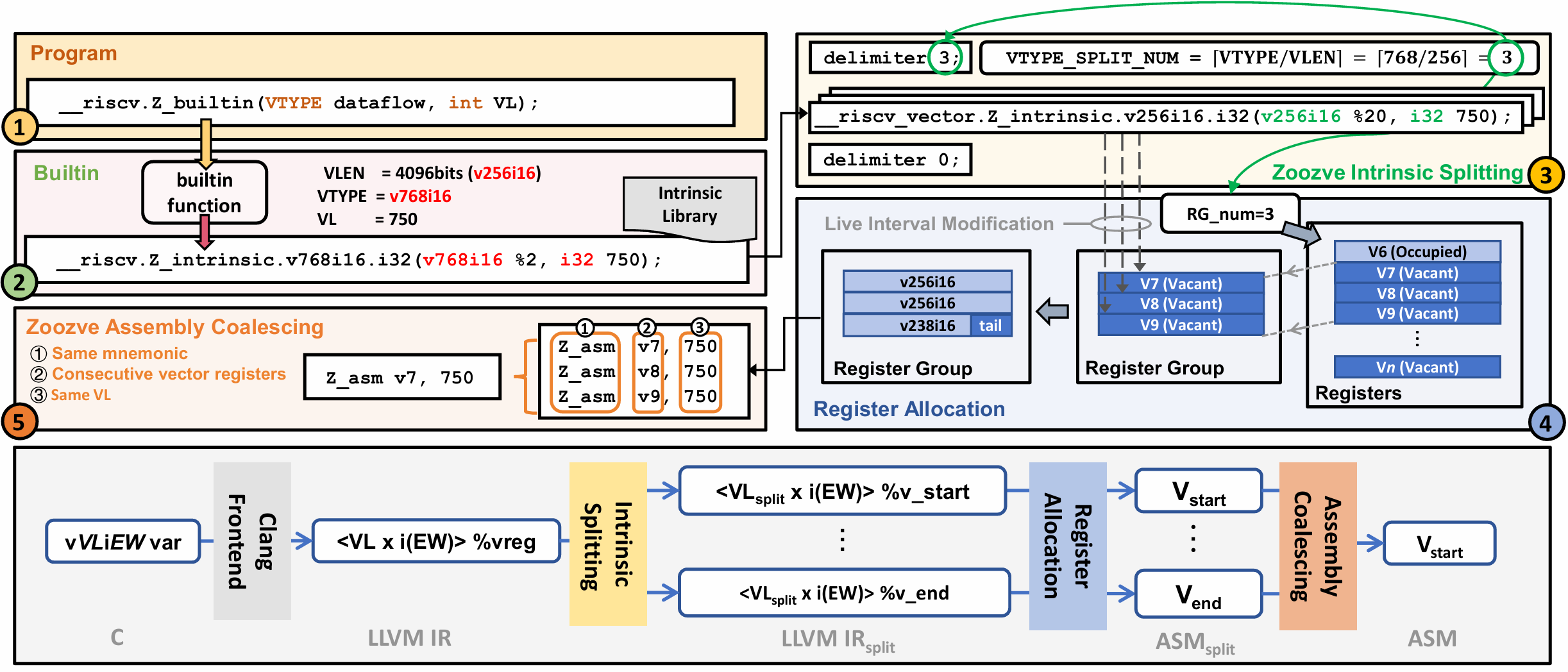

At the 26th ACM SIGPLAN/SIGBED International Conference on Languages, Compilers, and Tools for Embedded Systems (LCTES ‘25), we proposed Zoozve, a novel RISC-V vector extension that eliminates the need for strip-mining in long-vector processing. Zoozve supports arbitrary vector register grouping and features a data-adaptive register allocation strategy, significantly reducing register pressure. Backed by a custom LLVM-based compiler toolchain and SystemVerilog hardware implementation, Zoozve achieves up to 344× reduction in dynamic instruction count in FFT workloads with only a 5.2% area overhead. This advancement opens new directions for flexible and efficient vector computing in wireless and AI domains.

Check out our paper at : https://dl.acm.org/doi/abs/10.1145/3735452.3735526