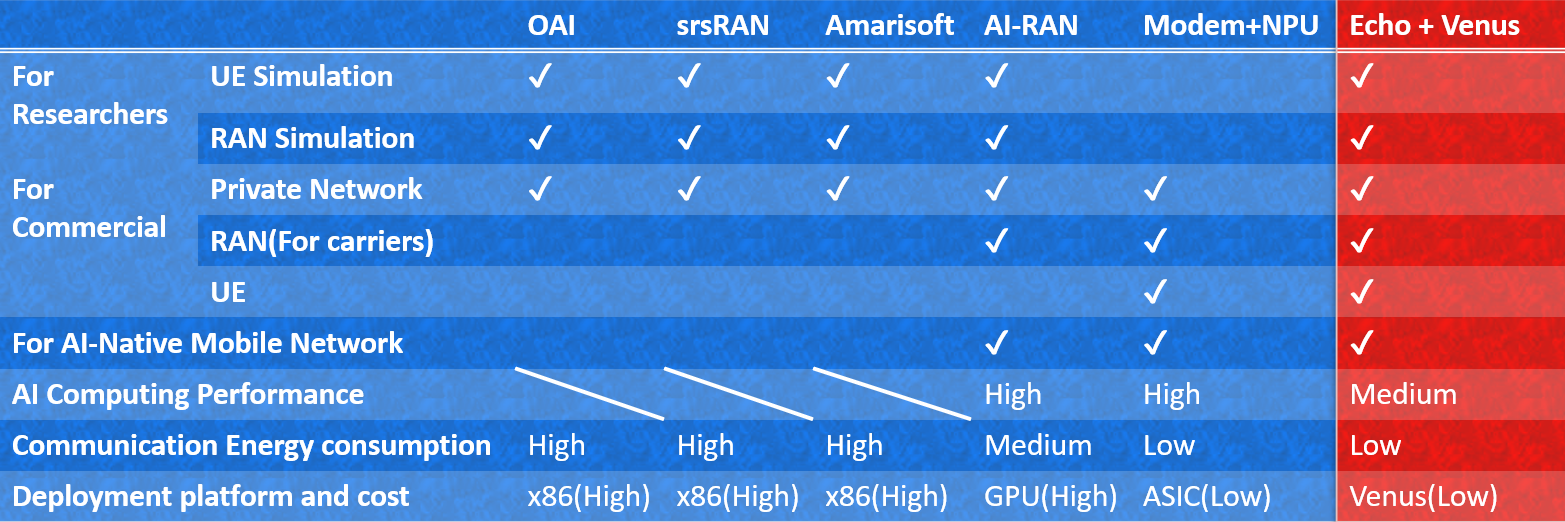

1. ACE-Echo+Venus vs Other Solutions

· Compared Solutions

OAI, srsRAN, Amarisoft, AI-RAN, Modem+NPU, ACE-Echo+Venus

· 🚩 Key Advantages

○ Supports UE simulation and RAN simulation in research scenarios, covering commercial private networks, carrier-grade RAN, and full-process UE adaptation

○ AI computing performance meets mobile communication needs, energy consumption outperforms x86/GPU solutions, and Venus-based deployment costs are lower

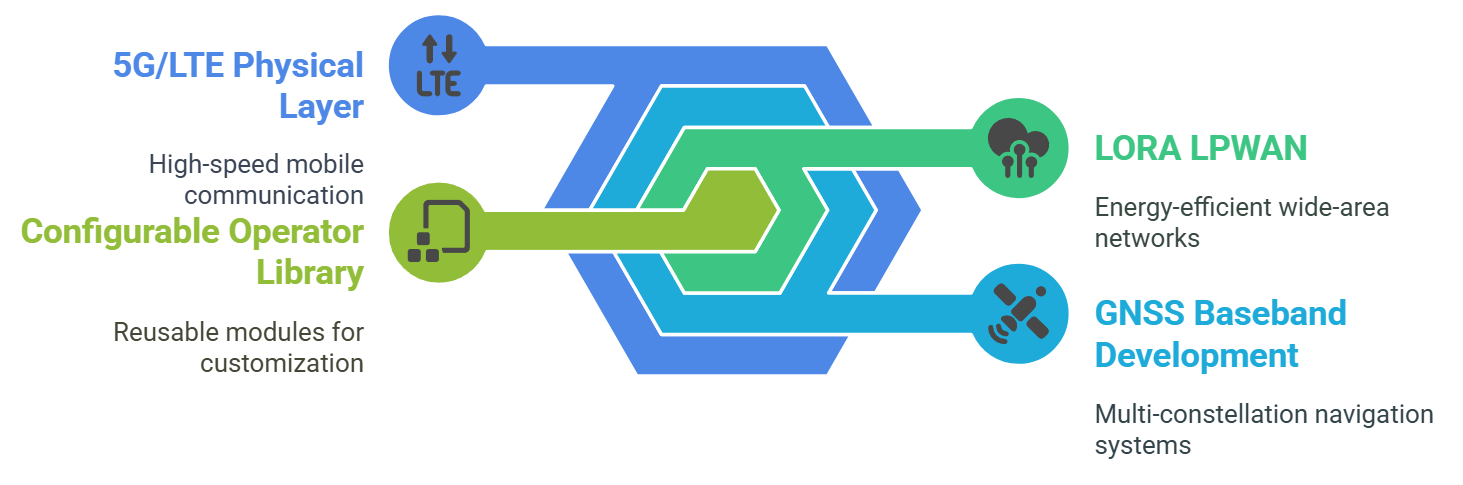

2. Comprehensive Communication Protocol Support

· 📶5G/LTE Physical Layer

Supports OFDM modulation/demodulation, FFT/IFFT (up to 4096 subcarriers), polar coding/decoding, rate matching, scrambling/descrambling, channel estimation (LS/MMSE), and MIMO beamforming, compliant with 3GPP-standard procedures (e.g., random access, cell search).

· 📡GNSS Baseband Development

Enables signal acquisition, tracking, carrier phase recovery, pseudorange processing, and multi-constellation fusion for GPS, BeiDou, etc., with low-power modes for IoT and automotive applications.

· 📍LORA Low-Power Wide-Area Networks (LPWAN)

Optimized for chirp modulation/demodulation, spreading factors (SF7-SF12), adaptive data rate (ADR) control, and interference mitigation algorithms, with energy-efficient processing via Venus vector instructions.

· Configurable Operator Library

Provides reusable operator modules (e.g.,fft_4096, polar_decoder) configurable via Python APIs or DSL scripts.

3. Flexible Development and Deployment

· Multi-Language Support

○ Python API: High-level interface for rapid prototyping (e.g., script-based 5G-LTE uplink simulation).

○ DSL (Domain-Specific Language): Visual workflow editor for defining task DAGs, ideal for complex protocol design.

○ C/C++: Low-level access for optimizing performance-critical modules (e.g., real-time control loops).

· Multi-Hardware Targets

○ Venus Processor: Native support for RISC-V domain-specific hardware, with cycle-accurate simulation via Echo.

○ CPU/GPU: Fallback for general-purpose computing in debugging or resource-constrained environments.

○ FPGA/ASIC: Supports RTL export for hardware acceleration (coming in v1.0).

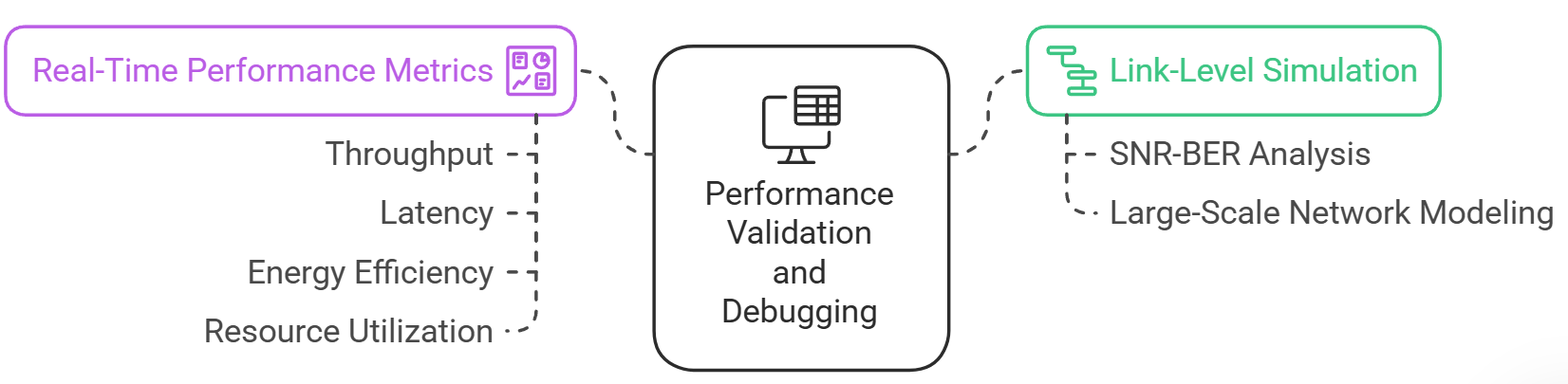

4. Performance Validation and Debugging

· Link-Level Simulation

Echo simulator provides side-by-side floating-point (reference) and fixed-point (hardware-ready) result comparison, supporting SNR-BER analysis and large-scale network modeling (e.g., 100+ UE simulations).· Real-Time Performance Metrics

Monitors throughput (bps/Hz), latency (cycles/bit), energy efficiency (pJ/bit), and resource utilization (vector lane occupancy, memory bandwidth), generating FPGA resource estimates and ASIC power consumption reports.